Analog Basics – Part 1: SAR Analog-to-Digital Converters

Contributed By DigiKey's North American Editors

2020-04-15

Editor’s Note: Analog-to-digital converters (ADCs) connect the analog to the digital world and so are a fundamental component of any electronic system that connects to the real world. They are also a key determining factor of a system’s performance. This series explores the fundamentals of ADCs, their various types, and their application. Here, in Part 1 of this series on analog basics, successive approximation register (SAR) ADCs will be discussed. In Part 2 will discuss delta-sigma (ΔƩ) converters. Part 3 looks at pipeline ADCs. Part 4 shows how delta-sigma ADCs can generate ultra-low noise results. Part 5 explores difficult input driving issues for SAR ADCs.

It’s still an analog world, so to get sensed information into the digital domain, some kind of conversion needs to take place. This heavy lifting is primarily reserved for the analog-to-digital converter (ADC). Over the years, the three ADC topologies that have successfully risen to prominence are the successive approximation register (SAR), the sigma-delta (S-D), and the pipeline ADC. All three ADC topologies are profoundly different in order to operate in different frequency ranges to service everything from low-frequency sensor applications up to higher frequency LiDAR or satellite communications, and beyond.

The SAR ADC was the first converter to go mainstream. Over time, this converter topology appeared across a variety of applications, including process control, medical, and early digital audio systems. These applications benefit from the SAR ADC’s output conversion ranges of 8 bits to 20 bits. However, the SAR ADC’s claim to fame is that it captures a snapshot of the analog input signal, using multiple signal snapshots to paint a picture over time.

This article briefly describes the signal chain that surrounds the SAR ADC. From there, it delves into this ADC topology with an analysis of the fundamental input stage that is responsible for the ADC’s snapshot action. The article then introduces example SAR ADC solutions—the AD7625BCPZ and AD4020BCPZ-RL7 from Analog Devices—focusing on the ADC4020BCPZ-RL7’s internal analog-to-digital conversion mechanics. Key specs for a suitable data acquisition system are also provided.

The SAR ADC's analog signal chain

The SAR ADC appears in systems such as automatic test equipment, machine automation, medical equipment, and precision data acquisition. With all SAR ADC applications, there is an analog signal that requires a digital representation with modest 8 to 20-bit resolution, with sampling from near DC to 15 megasamples per second (MSPS) (at the time of this writing).

The SAR ADC is very capable of operating without an analog front-end (AFE) signal chain. However, if the designer’s job is also to successfully present a signal at the SAR ADC’s front-end, there is more likely a requirement for a degree of signal conditioning (Figure 1).

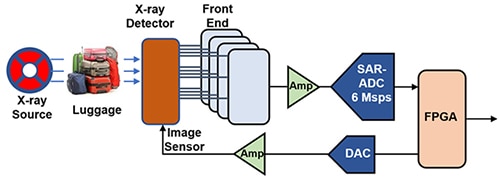

Figure 1: This sample SAR ADC signal chain includes an x-ray detector, AFE, amplifier driver, Analog Device’s AD7625BCPZ 6 MSPS converter, and a digital receptacle for the conversion results (the FPGA). (Image source: DigiKey)

Figure 1: This sample SAR ADC signal chain includes an x-ray detector, AFE, amplifier driver, Analog Device’s AD7625BCPZ 6 MSPS converter, and a digital receptacle for the conversion results (the FPGA). (Image source: DigiKey)

In the Figure, an x-ray source sends a signal through the luggage to the x-ray detector. The x-ray device’s job is to construct a complete image of the luggage in a short period of time to reduce traveler frustration.

The front-end takes the detector signal and performs signal conditioning functions such as analog gain and level shifting. The signal is then presented to the SAR ADC, which in this case is the AD7625BCPZ from Analog Devices.

The amplifier prior to the SAR ADC provides appropriate stability, usually with a first-order low-pass filter between the amplifier and SAR ADC. The SAR ADC is capable of sampling at up to 6 MSPS—one sample every 167 nanoseconds (ns)—to accommodate multiple snapshots in a short period of time.

SAR ADC input stage’s core simplified

The SAR ADC has gone through numerous enhancements and improvements over time, but in all cases, the primary activity during the conversion period is charge redistribution—one of the most common implementations of the successive approximation ADC. Also, with the SAR ADC, there is the added bonus of zero latency, unlike the S-D and pipeline converter.

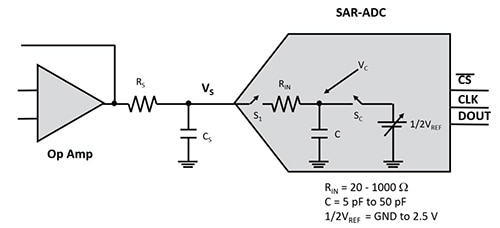

At the simplest level, it’s easy to see where the signal snapshot occurs. The SAR ADC input core contains an input signal acquisition switch (S1), a capacitive array, a conversion switch (SC), and an internal reference voltage (½ VREF) (Figure 2).

Figure 2: An operational amplifier (op amp), with an output stabilizing filter, driving a SAR ADC. (Image source: DigiKey)

Figure 2: An operational amplifier (op amp), with an output stabilizing filter, driving a SAR ADC. (Image source: DigiKey)

The operation of the SAR ADC core is as follows:

- S1 opens, SC closes: This disconnects the input stage from the analog signal source.

- The charge on C is re-calibrated by ½ VREF. This re-calibration brings the SAR ADC back to ground zero.

- Then S1 closes, SC opens: Now the device is connected to the input analog signal.

- The SAR ADC acquires the input signal, VS, over a predetermined acquisition time. This acquisition time allows for the S1 and SC switching noise and amplifier’s sudden exposure to capacitor loading and switching noise.

- Then S1 opens: This is the exact instance where the signal snapshot occurs.

- The SAR ADC converts the signal at VC to its digital representation. The time taken to do this is the “conversion time.”

SAR ADC input stage’s core details

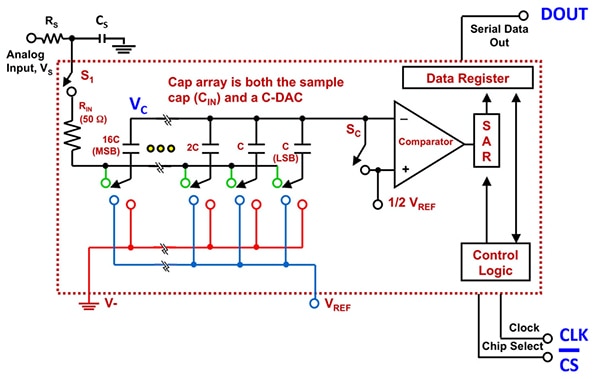

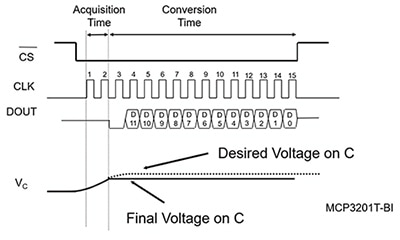

The conversion core engages in charge redistribution of the captured signal at VC. The orchestration of the converter’s charge redistribution occurs in the core, gated by the clock. From this process, each clocked digital output code arrives at the DOUT output of the SAR ADC (Figure 3).

Figure 3: A 4-bit SAR ADC curtain has a full array of digitally weighted capacitors: 16C, 8C, 4C, 2C, and two Cs. (Image source: DigiKey)

Figure 3: A 4-bit SAR ADC curtain has a full array of digitally weighted capacitors: 16C, 8C, 4C, 2C, and two Cs. (Image source: DigiKey)

As a first step during the conversion, the SAR ADC algorithm determines the most significant bit (MSB). The SAR ADC starts to test the signal magnitude compared to ½ VREF by switching the bottom of the 16C capacitor between the V- and VREF comparator inputs. The next comparison in the SAR ADC conversion line is testing 8C (not shown) against ½ VREF, followed by the test of 4C, etc.

SAR ADC output conversion details

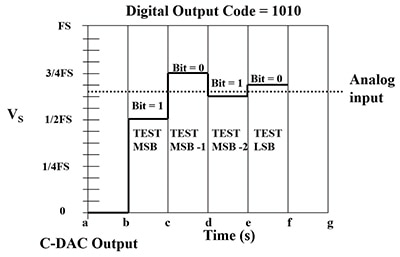

The MSB decision is immediately transmitted through the DOUT pin, and the MSB switch stays frozen, while the MSB 1 decision is made. The SAR ADC carries this algorithm through to the final selection of the least significant bit (LSB) (Figure 4).

Figure 4: The 4-bit SAR ADC clocks the conversion algorithm through bit decisions and transmits those decisions through the DOUT pin (shown in Figure 3). (Image source: DigiKey)

Figure 4: The 4-bit SAR ADC clocks the conversion algorithm through bit decisions and transmits those decisions through the DOUT pin (shown in Figure 3). (Image source: DigiKey)

In Figure 4, the SAR ADC clocked bit decisions are made from the MSB down to the LSB. All conversion data continues to be immediately clocked out through DOUT in the upper right of Figure 3. A full throughput time typically requires ample time for signal acquisition and a clock cycle for each bit.

SAR ADC conversion challenges

The designer must be aware of the amount of signal settling time needed to ensure that the correct analog value is captured from conversion (Figure 5).

Figure 5: The conversion timing diagram of a 12-bit SAR DAC. Each complete conversion requires 16 clocks. (Image source: DigiKey)

Figure 5: The conversion timing diagram of a 12-bit SAR DAC. Each complete conversion requires 16 clocks. (Image source: DigiKey)

In Figure 5, the input signal, VC, has not reached its final desired voltage before the converter’s input switch opens. In this instance, the circuit designer has miscalculated the settling time of the amplifier input signal.

The AD4020BCPZ-RL7 20-bit, 1.8 MSPS SAR ADC eases signal acquisition complexity by offering an extended acquisition phase, while still maintaining the throughput rate. It has a low signal-to-noise ratio (SNR) of 100.5 dB.

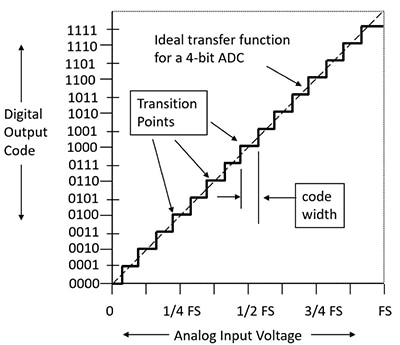

SAR ADC transfer function

The number of possible codes for ADCs is equal to 2N, where N is the number of bits. For example, a 4-bit converter has 24 or 16 separate codes available (Figure 6).

Figure 6: The transfer function, or graph of the digital output code versus the analog input voltage of an ideal 4-bit SAR ADC, should be a straight line. (Image source: DigiKey)

Figure 6: The transfer function, or graph of the digital output code versus the analog input voltage of an ideal 4-bit SAR ADC, should be a straight line. (Image source: DigiKey)

Painting the picture

The throughput rate of the SAR ADC includes the acquisition time and conversion time to achieve throughput rates of up to 1.8 MSPS at 20-bit resolution from Analog Devices’ AD4020BCPZ-RL7. With the AD4020BCPZ-RL7’s throughput speed, it is possible to acquire multiple snapshots and create a digital picture rendering solution for machine automation and medical equipment.

Conclusion

Used in applications from process control to medical and consumer, the SAR ADC continues to prove worthy with its signal snapshot capability and constantly improving resolution and speed. The SAR ADC at this point in time comes with resolutions from eight to 20 bits, with throughput rates up to 15 MSPS. One example, the AD4020BCPZ-RL from Analog Devices, offers low noise, high speed, and 20 bit, 1.8 MSPS precision. However, SAR ADC converter architecture is not done yet. There is more to come.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.